各种数字逻辑集成电路简介

RTL电路:一种由电阻和晶体管组合的逻辑电路,判断逻辑准位的方式是以输入端回路电流特性而定,当输入的电压VI低于晶体管导通电压时,就没有导通电流IB,晶体管C-E间成开路状态(截止),若输入的电压Vi高于晶体管导通电压时,而且电压越高C-E间导通就越多,换句话说这种逻辑族的的逻辑输出准位会受到输入准位的影响,所以使用时输入的逻辑准位必需保持足以让RTL能够截止或饱和的电压,才能保证下一级的逻辑电路能够正常判断,因此这已是一个被淘汰的逻辑族。838电子

[!--empirenews.page--]DTL电路[/!--empirenews.page--]DTL电路

DTL是一种晶体管电路加上二极管所设计的逻辑电路,它利用了二极管正向导通电压(约0.7V)的特性,提高逻辑电路VIH的准位电压,以及在晶体管基极加上负的偏压,当二极管电路断路时能够迅速使晶体管截止 改善了RTL输入电压对输出逻辑准位的不良影响,但是需要正负双电源的设计,目前也不见有数字系统采用这逻辑电路了。

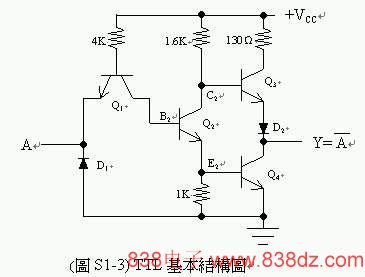

[!--empirenews.page--]TTL电路[/!--empirenews.page--]TTL电路

TTL以晶体管做为逻辑判断及逻辑输出的主要组件,输入端的电压低于0.8V为VIL,高于2.0V为VIH,这两个电压点之间的范围是一个逻辑准位的不明确区,设计电路时要避免有此范围的电压输入。TTL的输出端由两个串接的晶体管负则输出逻辑准位电压,Q3负责接通VCC,Q4负责接通地电位,使得VOH保证大于2.4V,VOL保证小于0.4V,逻辑“1”与“0”间更为明显,变化也较RTL、DTL迅速。由于要保证输入及输出的逻辑界定,电源必须为固定值,以74为编号的是商用IC,电源为5V,容许误差为±0.25V,工作温度范围为℃到7℃,54为编号的是军用IC,电源也是为5V,误差可以大一点为±0.5V,工作温度范围为-55℃到125℃。838电子

TTL发展至今以已有多种改良产品,以表格方式介绍及比较于下:

| TTL型别 | IC编号 | VOH | VIH | VOL | VIL | 传递 延迟 | 功率 消耗 |

| 标准型 | 74xx | 2.4V | 2.0V | 0.4V | 0.8V | 9 nS | 10 mW |

| 低功率 | 74Lxx | 2.4V | 2.0V | 0.3V | 0.8V | 33 nS | 1 mW |

| 高速型 | 74Hxx | 2.4V | 2.0V | 0.4V | 0.8V | 6 nS | 23 mW |

| 肖特基(Schottky) | 74Sxx | 2.7V | 2.0V | 0.5V | 0.8V | 3 nS | 23 mW |

| 低功率肖特基 | 74LSxx | 2.7V | 2.0V | 0.5V | 0.8V | 9.5 nS | 2 mW |

传递延迟:输入逻辑准位后到输出反应正确所需时间,此时间越短逻辑电路反应速率越快。

功率消耗:电路工作时所消耗的电能,此值越小越省电。

标准型、低功率、高速型差异在于电路中使用电阻的阻值,以标准型做比较时低功型率较大高速型较小,而电阻大者功率消耗较小,但传递延迟较大。

肖特基(Schottky)型TTL:将晶体管全部改采肖特基晶体管的TTL(图S1-5),肖特基晶体管是一种在集-射极间加有肖特基二极管的晶体管,如图S1-4所示,肖特基二极管的切入电压约0.3V,晶体管的VBE约0.7V,VCE=VBE-VBC=0.4V而晶体管之饱和电压VCE(sat)=0.2V,故晶体管之VCE 下降至0.4V时,IB被肖特基二极管分流不再进入晶体管基极,因此肖特基晶体管不会进入饱和区,所以交换速率较快。

[!--empirenews.page--]CTL电路[/!--empirenews.page--]CTL电路

互补式晶体管逻辑闸(Complementary Transistor Logic ; CTL)的电路特征,是拥有一个集极回受偏压的设计,如下图中的Q3偏压电路可以针对与它并接的晶体管做互补的动作,将Vf调节在某个范为之内,透过射极随耦电路(Q4)的输出与其它CTL电路相接时,这个电压(Vf-0.7V)高态时不会造成输入端晶体管(本例为Q1、Q2)饱和,低态时亦不会造成晶体管截止,所以CTL是属于非饱和快速型的逻辑族,主要用在大型计算机的设计中。

[!--empirenews.page--]ECL电路[/!--empirenews.page--]ECL电路

射极耦合逻辑闸(Emitter Coupled Logic;ECL),利用了差动放大器的电流互补特性,使其输出因为差动放大器的电流转移产生逻辑准位,所以又被称为电流式逻辑(Current-Mode Logic;CML)。

图S1-7中的Q3与Q2或Q1构成差动放大器,若Q2及Q1之输入逻辑准位为“0”,则Q2、Q1截止,使得C3电压为0V,此时共射极电流IE全部流经Q3, 300Ω的电压降为2.8178mA?00Ω=0.845V,则C3电压为0-0.845= -0.845V。反之,当Q2或Q1之输入逻辑准位有一者为“1”,则共射极电流IE会全部转移至Q2或Q1输入为“1”的那一个,因此C2电压转为-0.845V,C3电压转为0V,-0.845V与0V经射极随耦电路(Q4、Q5)输出后约为-1.5V及-0.7V即为ECL的VOL及VOH。

ECL工作时,从Q1、Q2、Q3 的VCE最小电压为VC-VE = (-0.845V)-( -1.875V)=1.03V,可以得知电路内的晶体管并不会进入饱和区(VCE =0.2V),所以是一种非饱和逻辑,交换速率可很快,传递延迟仅2nS,但噪声免疫力只有175mV左右。

ECL使用负电源,还有两个互补输出X及Y分别为非反相及反相的端子,由于采用射极随耦输出,输出端可以接在一起构成接线或门,这是一个免费的或门(注), 这些都是它的特色。

[!--empirenews.page--]MOS逻辑电路[/!--empirenews.page--]MOS逻辑电路

MOS逻辑电路的主要原件是金属-氧-半导体形成的场效晶体管 (Metal-Oxide-Semiconductor Field-Effect Transistor ;MOSFET),它是靠电压场促使端点导通的组件,分为增强型及衰减型两种,但MOS逻辑电路采用增强型MOSFET来设计电路,增强型MOSFET又分为N-MOS及P-MOS,图S1-10a是N-MOS的符号,图S1-10b是P-MOS的符号。N-MOS在电路中加入正电压促使源极与汲极导通,P-MOS在电路中加入负电压或零电压促使源极与汲极导通,电压的大小决定源极与汲极间电阻的大小,完全导通约1kΩ,开路时约1010Ω,所以MOS可当作开关或电阻组件,如图S-10c所示。图S1-11为N-MOS非门电路,可以看到上方的N-MOS做为电阻,下方的N-MOS做为开关,当A为正极性电压时导通,为零电压时开路。

由于MOS可以构成开关或电阻组件,作为数字逻辑电路制成较简单,而且体积也较小,因此很多大型及超大型的数字集成电路都采用MOS组件,例如计算机的动态随机存取内存(DRAM)、单芯片微电脑等等。

[!--empirenews.page--]CMOS逻辑电路[/!--empirenews.page--]CMOS逻辑电路

以N-MOS及P-MOS做为开关,在电路中以互补方式动作,也就是当N-MOS接通时,P-MOS必成断路状态,反之当P-MOS接通时,N-MOS必成断路状态,这种电路结构就是CMOS(Complementary MOS)。CMOS逻辑系列是由美商RCA公司首先生产,以CD40或CD45为编号,而Motorola生产的CMOS则以MC40与MC145为编号,另外国际半导体公司(National Semiconductor Co.)依照74系列TTL的接脚做成的CMOS以74C为编号,因此7400与74C00接脚完全相同,但7400是TTL而74C00是CMOS。

图S1-12是CMOS构成的非门,从图中可知正常情况下,A端的电压极性只会影响P-MOS或N-MOS其中一个导通,所以任何时刻电源+VDD与地之间仅存在漏电电流,因此CMOS的消耗电流相当的低,约等于电源电压和漏电电流的乘积,通常在10nW,这是目前最省电的数字集成电路。